# Design of Inductor Winding Capacitance Cancellation for EMI Suppression

Shuo Wang, Member, IEEE, Fred C. Lee, Fellow, IEEE, and Jacobus Daniel van Wyk, Fellow, IEEE

Abstract—In this paper, the parasitics in both differential-mode (DM) and common-mode (CM) inductors are first discussed. The methods for both DM and CM inductor winding capacitance cancellation are then proposed. Prototypes are designed and tested, using a network analyzer. Finally, the prototypes are applied to practical power converters and electromagnetic interference (EMI) is measured. Both small signal measurement and practical EMI measurement prove that the proposed methods can efficiently reduce the effects of winding capacitance and therefore improve the inductor's filtering performance.

*Index Terms*—Electromagnetic interference (EMI) filter, EMI noise, winding capacitance, winding capacitance cancellation.

## I. INTRODUCTION

THE IMPEDANCE of an ideal inductor is proportional to frequency, so it is usually used as a filtering component to conduct the low-frequency (LF) signal and block the high-frequency (HF) noise. For power electronics applications, the electromagnetic interference (EMI) filter is usually a low-pass filter. In order to build a high performance filter, the inductor must maintain its inductive characteristics in the applicable frequency range. EMI standards specify the conducted EMI limit up to 30 MHz, so the inductor must suppress the noise within this frequency range. However, the parasitic capacitance of the inductor changes the behavior to capacitive at high frequencies. The filter is therefore no longer the expected low-pass filter.

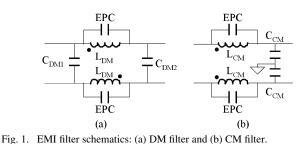

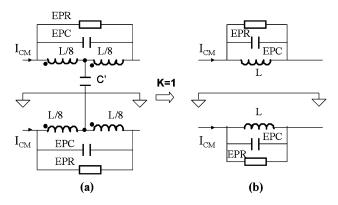

EMI filters are conventionally classified as differential-mode (DM) and common-mode (CM) filters based on the purpose of the filter in the noise suppression. The inductors of the filter are generally located in both the lines to attenuate either DM or CM noise. The capacitors are generally located across two lines or between the ground and two lines to attenuate DM or CM noise. Fig. 1(a) and (b) show the EMI filter schematics including the equivalent parallel capacitor (EPC) formed in the inductors.

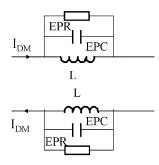

In Fig. 1, above the self-resonance frequency of the inductors, the filters would no longer be the expected low-pass filters. The HF noise would not be well attenuated because the inductors are bypassed by the EPC. The conventional lumped inductor model is shown in Fig. 2, where, the EPC represents the effects of turn-to-turn and turn-to-core capacitance. The equivalent parallel resistance (EPR) represents the effects of core loss and winding loss. The inductance L resonates with EPC

The authors are with the Bradley Department of Electrical and Computer Engineering, Virginia Polytechnic Institute and State University, Blacksburg, VA 24061 USA (e-mail: shwang6@vt.edu).

Digital Object Identifier 10.1109/TPEL.2006.882898

Fig. 2. Conventional inductor model.

at  $f = 1/(2\pi\sqrt{L \times \text{EPC}})$  and above that the inductor is not inductive but capacitive. In order to broaden the EMI filter operation frequency range, EPC should be minimized. For practical inductors, the parasitic model could be a little bit different from the conventional model. This paper will first investigate the capacitive parasitics in inductors, and then discuss the theory of inductor winding capacitance cancellation for both the DM and CM inductors. The prototypes are designed and built based on the theory. Finally, the measurements are carried out using a network analyzer to verify the approaches. The EMI measurements for practical power converters prove that the inductor's filtering performance is significantly improved using the proposed winding capacitance cancellation technique in the frequency band up to 30 MHz.

## II. THEORY OF WINDING CAPACITANCE CANCELLATION

## A. Parasitic Models of Inductors

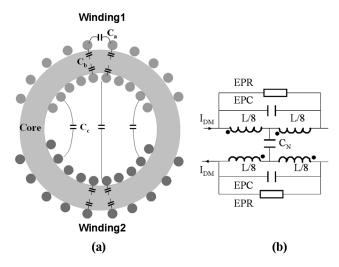

Two DM inductors in Fig. 1(a) can be two separate components or one integrated component. For separate inductors, each inductor can be represented by the conventional inductor model in Fig. 2 as shown in Fig. 3. However, if the two DM inductors are built on one core, Fig. 2 may not represent them very well because of the capacitive couplings between the two inductors. For this case, the two DM inductors can be coupled or non-coupled (if they are the leakage of CM inductors). Fig. 4(a) shows the cross section view of two coupled toroidal inductors. Three kinds of parasitic capacitance are shown in Fig. 4(a): turn-to-turn capacitance  $C_a$ , turn-to-core capacitance  $C_b$  and winding-to-winding capacitance  $C_c$  [8], [9]. The equivalent circuit of the inductor is shown in Fig. 4(b). The effects of  $C_a$  and  $C_b$  can be represented by EPC. The effects of  $C_b$  and  $C_c$  can be represented by an equivalent capacitor  $C_N$ .

EPR EPC

Manuscript received December 13, 2005. This work was supported by the Engineering Research Center Program of the National Science Foundation under NSF Award EEC-9731677. Recommended by Associate Editor F. Blaabjerg.

Fig. 3. Equivalent circuit for separated DM inductors.

Fig. 4. Parasitic capacitance between two inductor windings in two coupled DM inductors: (a) inductor structure and (b) equivalent circuit.

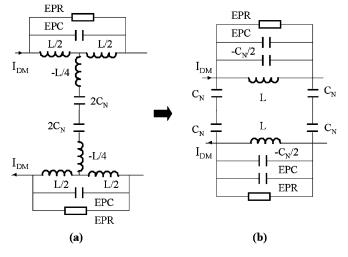

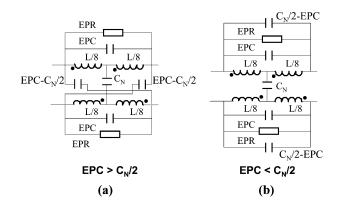

It is assumed that the two inductors (windings) are identical, so that all parasitic parameters are the same. The four inductors in Fig. 4(b) have the same inductance L/8 and the coupling coefficient is 1. Based on network theory, Fig. 4(b) can be decoupled to Fig. 5(a) and is theoretically equivalent to the network shown in Fig. 5(b).

In Fig. 5(b), the effects of  $C_N$  on the two inductors are represented by two negative capacitances  $-C_N/2$  in parallel with two inductors, respectively. If the EPC is larger than  $C_N/2$ , the total of the equivalent winding capacitance is still positive. The parallel resonant frequency is given by (1). If the EPC is smaller than  $C_N/2$ , the total of the equivalent winding capacitance is negative. There is no parallel resonance between the inductance L and negative capacitance EPC –  $C_N/2$ . For this case, minimum impedance exists at the frequency given by (2).  $C_N$  can be easily determined via (1) and (2) after measuring the insertion voltage gains of inductors

$$f_1 = \frac{1}{2\pi\sqrt{L\left(\text{EPC} - \frac{C_N}{2}\right)}}\tag{1}$$

$$f_2 = \frac{1}{2\pi\sqrt{L\left(\frac{C_N}{2} - \text{EPC}\right)}}.$$

(2)

For the case when two DM inductors are the leakage of two CM inductors, they are not coupled. The effects of  $C_N$  can still be represented by the models in Fig. 5(b) as long as unit coupling coefficient between two half windings is assumed.

Fig. 5. Equivalent circuit for coupled DM inductors: (a) decoupled circuit and (b) final equivalent circuit.

Fig. 6. Equivalent circuit for coupled CM inductors: (a) equivalent circuit and (b) the final decoupled circuit.

For CM inductors in Fig. 6(a), since CM current does not flow through the parasitic capacitance between two inductors, there is no need to consider this parasitic capacitance. Each decoupled CM inductor can still be represented by the model in Fig. 2 as shown in Fig. 6(b).

## B. EPC Cancellation for DM Inductors

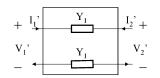

For the separated DM inductors in Fig. 3, it is assumed that the two DM inductors are exactly identical. If two inductors together with their parasitics are characterized as two equal admittances  $Y_1$  given by (3), the DM inductors can then be described by the network in Fig. 7. The Y parameters of this network and the relationship of port voltages and currents are given by

$$Y_1 = j\omega \times \text{EPC} + \frac{1}{\text{EPR}} + \frac{1}{j\omega L_{\text{DM}}}$$

(3)

$$Y_{mn} = \frac{I_m}{V_n} \bigg|_{V_m = 0}, (m, n = 1, 2)$$

$$(4)$$

$$\begin{pmatrix} I_1'\\ I_2' \end{pmatrix} = \begin{pmatrix} Y_{11} & Y_{12}\\ Y_{21} & Y_{22} \end{pmatrix} \begin{pmatrix} V_1'\\ V_2' \end{pmatrix}$$

$$= \begin{pmatrix} j\omega \times \text{EPC} + \frac{1}{\text{EPR}} + \frac{1}{j\omega L_{\text{DM}}} \end{pmatrix}$$

$$\times \begin{pmatrix} 1/2 & -1/2\\ -1/2 & 1/2 \end{pmatrix} \begin{pmatrix} V_1'\\ V_2' \end{pmatrix}.$$

(5)

Fig. 7. Characterization of DM inductors using two equal admittances.

Fig. 8. Network used to cancel EPC.

Fig. 9. Cancellation of inductor winding capacitance: (a) parallel of two networks and (b) equivalent network after EPC cancellation.

The trans-admittance  $Y_{12}$  and  $Y_{21}$  in (5), which represent the inductor's capability for signal transfer, should be as small as possible at HF since the inductor is supposed to suppress HF noise. The  $-j\omega \times \text{EPC}/2$  term in the trans-admittance, which represents the effects of winding capacitance, makes trans-admittance large at high frequencies, so it should be canceled in order to improve the inductor's HF performance. If a network can be found with a trans-admittance equal to  $j\omega \times \text{EPC}/2$ and this network can be paralleled with the network in Fig. 3, then the resultant network has a trans-admittance independent of EPC, since the Y matrix of two paralleled networks equals the sum of their Y matrixes. Fig. 8 shows a network having this property. Its Y matrix and the relationship between the port voltages and currents are shown in

$$\begin{pmatrix} I_1''\\ I_2'' \end{pmatrix} = \begin{pmatrix} j\omega \times \text{EPC}/2 & j\omega \times \text{EPC}/2\\ j\omega \times \text{EPC}/2 & j\omega \times \text{EPC}/2 \end{pmatrix} \begin{pmatrix} V_1''\\ V_2'' \end{pmatrix}.$$

(6)

After the network in Fig. 8 is paralleled with the DM inductors in Fig. 3, the resultant network is shown in Fig. 9(a) and its Y matrix is given by (7), shown at the bottom of the page.

In (7), EPC no longer exists in the trans-admittance; therefore it does not affect the HF performance of the inductors anymore. For self-admittance, since there is a  $j\omega \times \text{EPC}$  term, there is a

Fig. 10. Winding capacitance cancellation strategy: (a) EPC>  $C_N/2$  and (b) EPC<  $C_N/2$ .

shunt capacitance, with value equal to EPC, on both the input and output sides of the DM inductors. So, the parallel combination of the two networks not only cancels the effects of EPC, but also results in an equivalent shunt capacitor on both input and output sides, which builds a  $\pi$  type EMI filter as shown in Fig. 9(b).

For the coupled DM inductors in Figs. 4 and 5, if  $C_N/2$  is smaller than EPC, the total capacitance is positive. In order to cancel this positive capacitance, two capacitors with capacitance EPC –  $C_N/2$  should be diagonally connected to the two inductors (windings) as shown in Fig. 10(a), to cancel this positive equivalent winding capacitance. If the  $C_N/2$  is smaller than EPC, the total winding capacitance is negative. In order to cancel this negative capacitance, two capacitors with capacitance  $C_N/2$ -EPC should be paralleled with two inductors (windings), respectively, as shown in Fig. 10(b) to cancel this negative winding capacitance.

Since Fig. 5(b) is also the inductor model when the two DM inductors are formed by the leakage of the CM inductors, EPC cancellation approaches similar to those described in Fig. 10 also apply.

## C. EPC Cancellation for CM Inductors

CM inductors are a single-ended structure, so if an extra winding is allowed in the grounding path, the idea of EPC cancellation for DM inductors can also be applied here. In that case, two CM windings are in the power paths and the third winding, which may be reversely coupled to the other two windings, is in the grounding path. The small cancellation capacitors are diagonally connected between the two windings in the power lines and the third winding in the grounding path. If there is a DM capacitor on the input or output side, then only one cancellation capacitor is needed on either side, since the DM capacitor can balance the CM noise. Fig. 11 illustrates this.

$$\begin{pmatrix}

I_1 \\

I_2

\end{pmatrix} = \begin{pmatrix}

j\omega \times \text{EPC} + \left(\frac{1}{\text{EPR}} + \frac{1}{j\omega L_{\text{DM}}}\right)/2 & -\left(\frac{1}{\text{EPR}} + \frac{1}{j\omega L_{\text{DM}}}\right)/2 \\

- \left(\frac{1}{\text{EPR}} + \frac{1}{j\omega L_{\text{DM}}}\right)/2 & j\omega \times \text{EPC} + \left(\frac{1}{\text{EPR}} + \frac{1}{j\omega L_{\text{DM}}}\right)/2

\end{pmatrix} \begin{pmatrix}

V_1 \\

V_2

\end{pmatrix}$$

(7)

Fig. 11. Cancellation of EPC for CM inductors.

Fig. 12. Cancellation of winding capacitance for CM inductors: (a) two capacitors are connected to center taps of two windings, and (b) equivalent network, and (c) EPC canceled network.

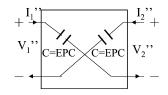

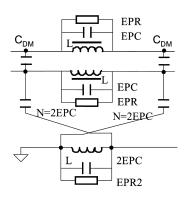

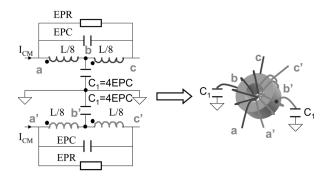

However, if the impedance is not allowed in the grounding path, the method proposed in [1] should be considered. A method using two small capacitors to cancel the effects of EPC is introduced for integrated CM EMI filters in [1]. The basic idea is shown in Fig. 12. The two windings of the CM inductors are center tapped and two grounded capacitors  $C_1$ are connected to the center taps as shown in Fig. 12(a). Its equivalent  $\pi$  network is shown in Fig. 12(b). The  $Z_e$  is given by

$$Z_e = \frac{j\omega L}{1 - \omega^2 L (\text{EPC} - C_1/4)}.$$

(8)

In (8), if  $C_1$  equal 4 × EPC, then  $Z_e = j\omega L$ , so that the circuit is equivalent to a  $\pi$  type filter without EPC, as shown in Fig. 12(c). The effects of EPC are then canceled. This method has been applied to integrated CM inductors successfully in a planar magnetic structure because the high coupling coefficient (> 0.9999) between two halves of one CM inductor winding is easy to achieve in planar structures. The conventional discrete CM inductors are not planar structure, so the coupling coefficient is not so high (< 0.999). As a result, the leakage inductance  $L_K$  of two half windings resonate with the introduced capacitance 4EPC at a frequency give by (9), which makes the CM inductors performance worse than the CM inductor without EPC cancellation at high frequencies [2]. In order to apply this idea to a conventional discrete CM inductor, the design of a discrete CM inductor with high coupling coefficient (> 0.9999)between two half windings is very critical.

$$f = \frac{1}{2\pi\sqrt{2L_K \text{EPC}}}.$$

(9)

Fig. 13. Measurement setup for the measurement using balanced network analyzer.

Fig. 14. Improvement of inductor performance with winding capacitance cancellation.

## III. DESIGN OF WINDING CAPACITANCE CANCELLATION

## A. Design of Winding Capacitance Cancellation for DM Inductors

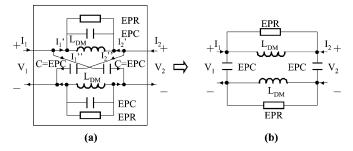

For the separated DM inductors, two toroidal cores, Kool M $\mu$  powder 77059 [7], are used in the experiment. The impedances of the inductor are first measured, and then the parameters are determined through curve fitting. The inductance of the two inductors is 42.34  $\mu$ H and 42.44  $\mu$ H. The winding capacitance EPC of the two inductors is 10.3 pF and 10.1 pF. The equivalent parallel resistance EPR of the two inductors is 10.9 k $\Omega$  and 10.7 k $\Omega$ . According to the analysis in Section II, the cancellation technique shown in Fig. 9 should be used. The cancellation capacitors used in the experiment are 9.9 pF and 10.2 pF.

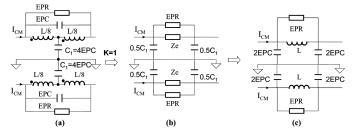

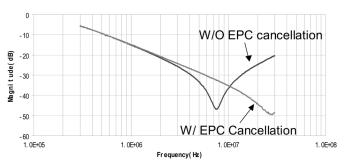

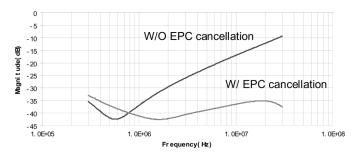

The measurement setup is shown in Fig. 13. An Agilent E5070B, four-port balanced ENA RF network analyzer [4] is used in the experiments. The measured differential insertion voltage gains (SDD21) with and without EPC cancellation are compared in Fig. 14. It is shown that there is a parallel resonance around 7.5 MHz for the original inductor. After the winding capacitance cancellation technique is applied, the resonant frequency increases to 29 MHz. As a result, the insertion voltage gain with winding capacitance cancellation is better than the original inductor above 10 MHz and a 29 dB improvement is achieved at 30 MHz.

For the second experiment, two DM inductors are coupled on one toroidal core, MPP 55308A2 [7]. The parameters of the inductor are determined by measurements. The inductance L of one winding is around 20  $\mu$ H. The winding capacitance EPC of one winding is 2.2 pF. The equivalent parallel resistance EPR of one winding is 3.2 k $\Omega$ . The parasitic capacitance  $C_N$  between two windings is 14.8 pF, which is determined by (2) via insertion voltage gain measurement. Because  $C_N/2$  is larger than EPC, the total winding capacitance is negative, -5.2 pF. In order to cancel it, two 5.2-pF capacitors should be paralleled with the

Fig. 15. Improvement of inductor filtering performance at high frequencies due to the EPC cancellation.

Fig. 16. Coupling coefficient of conventional CM inductor winding structure is not high enough.

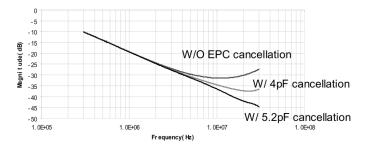

two windings respectively as described in Fig. 10(b). The measurement setup is same as that in Fig. 13. The measured differential insertion voltage gains with and without EPC cancellation are shown in Fig. 15.

In Fig. 15, for the case without EPC cancellation, the minimum impedance occurs at 11 MHz, which is predicted by (2). As a comparison, two 4 pF capacitors are first paralleled with the two windings respectively; and then two 5.2-pF capacitors are used. It is shown that 4 pF compensation is not enough; the best performance is obtained with 5.2 pF cancellation, because the winding capacitance is almost cancelled. There is 17 dB improvement at 30 MHz.

## *B.* Design of Winding Capacitance Cancellation for CM Inductors

For most cases, impedances are not preferred in the grounding path, so the concept in Fig. 12 is considered for the winding capacitance cancellation. For a conventional CM inductor structure, in order to implement the idea, the two windings must be center tapped. Two grounded cancellation capacitors are then connected to the center taps respectively, as shown in Fig. 16. The toroidal core of the inductors used in the experiment is Jmaterial from the Magnetics Company [7]. The parameters of the inductor are determined through measurements. The inductance of two windings is around 2.7 mH. The winding capacitance EPC of one winding is 5.8 pF. The equivalent parallel resistance EPR of one winding is 15 k $\Omega$ . Leakage inductance between two half windings is 4.24  $\mu$ H (K = 0.994). The cancellation capacitors have a capacitance of 24 pF.

Experiments are carried out to test the performance of the prototype. The setup is the same as in the previous experiment as shown in Fig. 13. The measured common mode insertion

Fig. 17. EPC cancellation is not good at HF due to leakage inductance for the conventional windings structure.

Fig. 18. Proposed winding strategy to increase the coupling coefficient of two half windings.

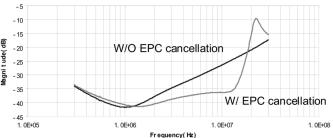

voltage gains with and without EPC cancellation are compared in Fig. 17.

In Fig. 17, from 1.25 to 18.5 MHz, the inductor performance is improved; however from 18.5 to 30 MHz, the performance is even worse. As predicted by (9), the peak around 23 MHz is the result of the resonance between the leakage inductance of two half windings and the cancellation capacitance. In order to guarantee the inductor's high frequency performance, the leakage inductance between the two winding halves must be minimized.

For a conventional CM inductor as shown in Fig. 16, the two winding halves do not have very high coupling coefficient because they are not at the same position. To achieve a high coupling coefficient, a bifilar winding as in Fig. 18 must be used. The leakage energy is now only stored in the air gap between two turns. Compared with the conventional winding strategy, the measured coupling coefficient is increased from 0.994 to 0.99995, which makes EPC cancellation possible for discrete CM inductors.

The toroidal core of the inductors used in the experiment is J material [7], which is same as that in Fig. 16. The parameters of the inductor are determined via measurements. The inductance of two windings is around 2.65 mH. The winding capacitance EPC of one winding is 10.1 pF. The equivalent parallel resistance EPR of one winding is 14.6 k $\Omega$ . Leakage inductance between two winding halves is 33 nH (K = 0.99995). The cancellation capacitors have a capacitance of 40 pF.

Although the proposed winding strategy introduces larger winding capacitance (10.1 pF versus 5.8 pF), the leakage inductance is greatly reduced. After the winding capacitance cancellation is applied, the inductor has much better performance than the previous case. The measured common mode insertion voltage gains with and without EPC cancellation is compared in Fig. 19.

In Fig. 19, the inductor's performance is greatly improved above 800 kHz compared with the case without EPC cancel-

Fig. 19. Insertion voltage gains with and without EPC cancellation.

Fig. 20. Using prototypes to build L type EMI filters: (a) DM filter and (b) CM filter.

lation. There is a 28-dB improvement at 30 MHz. Compared with the EPC cancellation in Fig. 17, the EPC cancellation in Fig. 19 has much better performance above 12 MHz. A 22-dB improvement is achieved at 30 MHz through the proposed winding strategy.

The bifilar winding structure proposed in Fig. 18 can also be used for the DM inductor EPC cancellation in Fig. 10 to prevent the possible resonance between  $C_N$  and the leakage inductance of two winding halves. For many of cases, the resultant resonance is above 30 MHz, which makes the resonance not as critical as that in CM inductors.

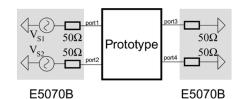

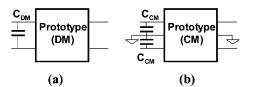

#### C. Applications to EMI Filters

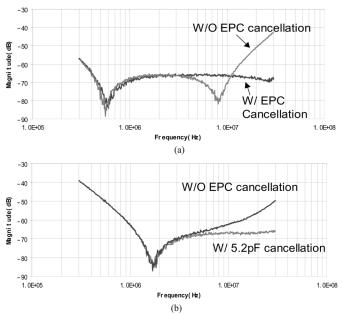

The inductor prototypes are then used with capacitors to build L type EMI filters, as shown in Fig. 20. A DM capacitor ( $C = 3.22 \ \mu\text{F}$ , ESL= 20.9 nH, ESR= 13.6 m $\Omega$ ) is first used with the non-coupled DM inductors in Fig. 14 as an L type DM EMI filter, as shown in Fig. 20(a). The measured differential insertion voltage gains with and without EPC cancellation are compared in Fig. 21(a). The performance is improved above 11 MHz and there is a 26 dB improvement at 30 MHz.

In the second experiment, a DM capacitor (C = 477 nF, ESL= 18.5 nH, ESR= 35.4 m $\Omega$ ), is used with the coupled DM inductors in Fig. 15 as an L type DM EMI filter, as shown in Fig. 20(a). The measured differential insertion voltage gains with and without EPC cancellation are compared in Fig. 21(b). The performance is improved above 5 MHz and there is a 16-dB improvement at 30 MHz.

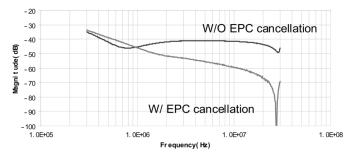

For the CM inductors in Fig. 19, two 2200-pF CM capacitors are used to build an L type CM filter, as shown in Fig. 20(b). The measured common mode insertion voltage gains with and without EPC cancellation are compared in Fig. 22. The performance is improved above 1 MHz and there is a 22-dB improvement at 30 MHz.

The proposed winding capacitance cancellation technique can also be used for other applications besides EMI filters. For example, for a dual boost PFC, two identical boost inductors are located on two power lines, so the winding capacitance

Fig. 21. Improvement of DM filter performance at high frequencies due to the EPC cancellation: (a) separated inductors and (b) coupled inductors.

Fig. 22. Improvement of CM filter performance at high frequencies due to the EPC cancellation.

cancellation technique introduced in Fig. 9 can be easily used to cancel the inductor winding capacitance. By applying winding capacitance cancellation to dual boost inductors, the HF DM noise source can be reduced [5]. The techniques may also used to cancel the DM winding capacitance in a transformer.

### **IV. EMI MEASUREMENTS**

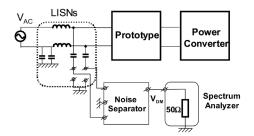

Because the measurements in Section III are carried out with small signal excitation and 50- $\Omega$  load and source impedances, it is necessary to verify the performance improvement for the inductors with current bias, large signal excitation, and a practical source and load. It is expected that the current bias does not affect HF noise reduction because HF noise flows through winding capacitance [6]. The prototypes in Figs. 14, 15, and 19 are finally tested in practical power converters. In Fig. 23, either DM or CM noise is measured for each prototype by using two line impedance stabilizing networks (LISNs), a noise separator [3], and an Agilent EMC7402A EMC analyzer. The measured data for the original inductors and EPC canceled inductors are compared in Figs. 24–26.

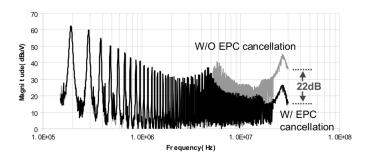

In Fig. 24, the power converter used for noise measurement is a flyback converter. The non-coupled DM inductor prototypes

Fig. 23. EMI measurement for the prototypes in a practical power converter.

Fig. 24. DM noise reduction for separated DM inductors with winding capacitance cancellation technique.

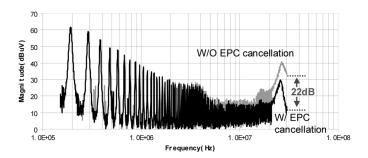

Fig. 25. DM noise reduction for coupled DM inductors with winding capacitance cancellation technique.

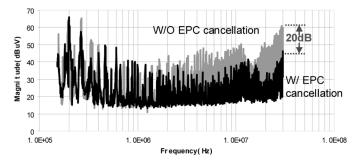

Fig. 26. CM noise reduction for CM inductors with winding capacitance cancellation technique.

in Fig. 14 are tested in the measurement. The noise with EPC cancellation has a lower value than that without EPC cancellation above 5 MHz. There is a 22-dB improvement at 30 MHz. In Fig. 25, the power converter is the same flyback converter as in Fig. 24. The coupled DM inductor prototypes in Fig. 15 are tested in the measurement. The noise with EPC cancellation has a lower value than that without EPC cancellation above

6 MHz. There is a 22-dB improvement at 30 MHz. In Fig. 26, the power converter used for noise measurement is a boost power factor correction (PFC) converter. The CM inductor prototypes in Fig. 19 are tested in the measurement. The noise with EPC cancellation has a lower value than that without EPC cancellation above 1 MHz. There is a 20-dB improvement at 30 MHz.

#### V. CONCLUSION

This paper discussed the winding capacitance cancellation techniques for both DM and CM inductors. The theory is first developed and refined from existing technologies. The prototypes are then designed, built, and measured using a network analyzer. Finally, the prototypes are used in practical power converters for EMI measurement. It is shown that the proposed technique can efficiently reduce the winding capacitance of inductors by simply improving winding structures and using two small capacitors. EMI measurements prove that it can significantly reduce HF noise.

## REFERENCES

- R. Chen, J. D. van Wyk, S. Wang, and W. G. Odendaal, "Improving the characteristics of integrated EMI filters by embedded conductive layers," *IEEE Trans. Power Electron.*, vol. 20, no. 3, pp. 611–619, May 2004.

- [2] R. Chen, "Integrated EMI Filters for Switch Mode Power Supplies," Ph.D. dissertation, Virginia Tech, Blacksburg, 2004.

- [3] S. Wang, F. C. Lee, and W. G. Odendaal, "Characterization, evaluation and design of noise separator for conducted EMI noise diagnosis," *IEEE Trans. Power Electron.*, vol. 20, no. 4, pp. 974–982, Jul. 2005.

- [4] Agilent E5070B/E5071B ENA Series RF Network Analyzers User's Guide, 5th ed. Palo Alto, CA: Agilent Technologies, 2004.

- [5] S. Wang, F. C. Lee, and W. G. Odendaal, "Single layer iron powder core inductor model and its effects on boost PFC EMI noise," in *Proc. IEEE Power Electron. Spec. Conf.*, Jun. 15–19, 2003, vol. 2, pp. 847–852.

- [6] ——, "Characterization and parasitic extraction of EMI filters using scattering parameters," *IEEE Trans. Power Electron.*, vol. 20, no. 2, pp. 502–510, Mar. 2005.

- [7] Powder Cores Design Manual, Std. Magnetics, 2005.

- [8] A. Massarini and M. K. Kazimierczuk, "Self-capacitance of inductors," *IEEE Trans. Power Electron.*, vol. 12, no. 4, pp. 671–676, Jul. 1997.

- [9] A. Baccigalupi, P. Daponte, and D. Grimaldi, "On a circuit theory approach to evaluate the stray capacitances of two coupled inductors," *IEEE Trans. Instrum. Meas.*, vol. 43, no. 5, pp. 774–776, Oct. 1994.

Shuo Wang (S'03–M'06) received the B.S.E.E. degree from Southwest Jiaotong University, Chengdu, China, in 1994, the M.S.E.E. degree from Zhejiang University, Hangzhou, China, in 1997, and the Ph.D. degree from the Center for Power Electronics Systems (CPES), Virginia Polytechnic Institute and State University (Virginia Tech), Blacksburg, in 2005.

Since 2005, he has been a Research Assistant Professor with the Center for Power Electronics Systems, Virginia Tech. From 1997 to 1999, he was with ZTE Telecommunication Corporation, Shenzhen, China,

where he was a Senior R&D Engineer and responsible for the development and support of the power supply for wireless products. In 2000, he worked at UT-starcom Telecommunication Corporation, Hangzhou, China, where he was responsible for the development and support of the optical access networks. He has been a Research Assistant Professor at CPES. He holds one U.S. patent and has two U.S. patents pending.

Dr. Wang received the 2005 Annual Best Paper Award from the IEEE TRANSACTIONS ON POWER ELECTRONICS and the William M. Portnoy Award for the paper published in the IEEE IAS Annual Conference in 2004. He has served as an Associate Editor for the Power Electronics Devices and Components Committee for the IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS since 2005.

**Fred C. Lee** (S'72–M'74–SM'87–F'90) received the B.S. degree in electrical engineering from National Cheng Kung University, Taiwan, R.O.C., in 1968 and the M.S. and Ph.D. degrees in electrical engineering from Duke University, Durham, NC, in 1971 and 1974, respectively.

He is a University Distinguished Professor with Virginia Polytechnic Institute and State University (Virginia Tech), Blacksburg, and prior to that he was the Lewis A. Hester Chair of Engineering at Virginia Tech. He directs the Center for Power Electronics

Systems (CPES) (a National Science Foundation engineering research center whose participants include five universities and over 100 corporations). In addition to Virginia Tech, participating CPES universities are the University of Wisconsin-Madison, Rensselaer Polytechnic Institute, North Carolina A&T State University, and the University of Puerto Rico-Mayaguez. He is also the Founder and Director of the Virginia Power Electronics Center (VPEC). His research interests include high-frequency power conversion, distributed power systems, space power systems, power factor correction techniques, electronics packaging, high-frequency magnetics, device characterization, and modeling and control of converters. He holds 30 U.S. patents, and has published over 175 journal articles in refereed journals and more than 400 technical papers in conference proceedings.

Dr. Lee received the Society of Automotive Engineering's Ralph R. Teeter Education Award (1985), Virginia Tech's Alumni Award for Research Excellence (1990), and its College of Engineering Dean's Award for Excellence in Research (1997), in 1989, the William E. Newell Power Electronics Award, the highest award presented by the IEEE Power Electronics Society for outstanding achievement in the power electronics discipline, the Power Conversion and Intelligent Motion Award for Leadership in Power Electronics Education (1990), the Arthur E. Fury Award for Leadership and Innovation in Advancing Power Electronic Systems Technology (1998), the IEEE Millennium Medal, and honorary professorships from Shanghai University of Technology, Shanghai Railroad and Technology Institute, Nanjing Aeronautical Institute, Zhejiang University, and Tsinghua University.

**Jacobus Daniel van Wyk** (F'90) received the M.Sc. Eng. degree from the University of Pretoria, Pretoria, South Africa, in 1966, the Dr.Sc.Tech. degree (with honors) from the Technical University of Eindhoven, Eindhoven, The Netherlands, in 1969, and the D.Sc. degree (with highest honors) from the University of Natal, Natal, South Africa, in 1996.

He has worked with the S.A. Iron and Steel Corporation, the University of Pretoria, and the technical and scientific staff of the University of Eindhoven, from 1961 to 1971. From 1971 to 1995, he was a

chaired Professor of Electrical and Electronic Engineering at the Rand Afrikaans University, Johannesburg, holding Chairs in Electronics and in Power Electronics until 1992. He founded the Industrial Electronics Technology Research Group in the Faculty of Engineering in 1978 and directed this unit until 1999. Since July 1995, he has held a special University Council Research Chair in Industrial Electronics at Rand Afrikaans University, since 2000 in a part-time capacity. He joined The Bradley Department of Electrical and Computer Engineering, Virginia Polytechnic Institute and State University (Virginia Tech), Blacksburg, in January 2000, where he is the J. Byron Maupin Professor of Engineering. He is also with the National Science Foundation Engineering Research Center for Power Electronics Systems, Virginia Tech, where he leads the High Density Integration Research Thrust. He has worked and published in the fields of semiconductors, microelectronics, electric materials, electromechanical energy conversion, electric drives, power electronics, industrial electronics, control, alternative energy systems, electric vehicles, and many diverse applications in industry, mining, transportation, and electrical energy supply systems. His present research interest is in integrated electronic power processors.

Dr. van Wyk is a Fellow of the South African Institute of Electrical Engineers. He received 20 prize papers awards including 11 IEEE prize paper awards, the IEEE William E. Newell Power Electronics Award in 1995, an IEEE Third Millennium Medal in 2000, and a range of other awards from IEEE Societies as well as from the South African Institute of Electrical Engineers. He is active in several capacities within the IEEE and its Societies, as well as in other scientific and engineering organizations, especially regarding publishing and organization of conferences. He has served as Editor-in-Chief of the IEEE TRANSACTIONS ON POWER ELECTRONICS since 2002.